# M21012/M21011/M21001

# Quad Multi-Rate CDR (42 Mbps - 3.2 Gbps)

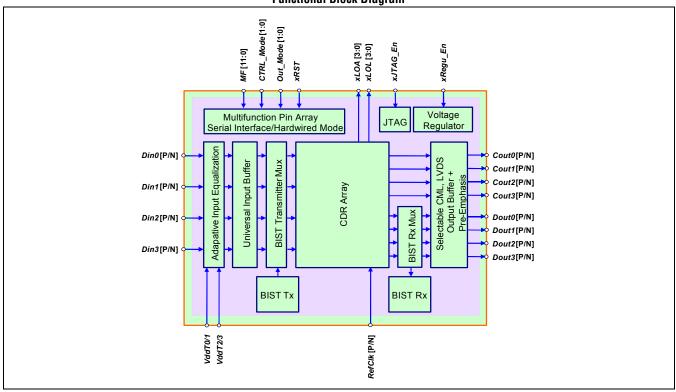

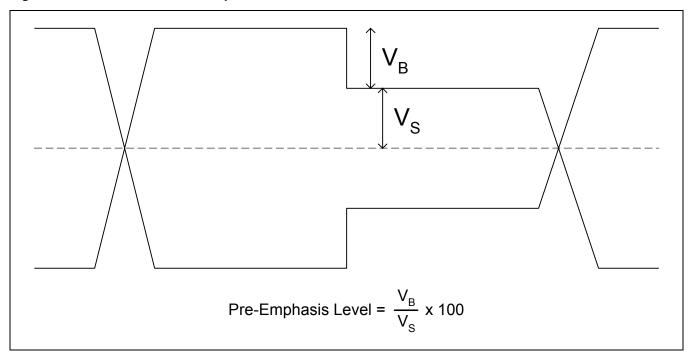

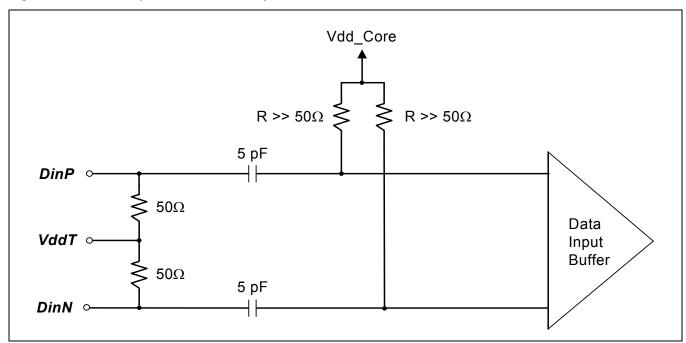

The M21012 is a high-performance quad multi-rate clock and data recovery (CDR) array, optimized for multi-lane telecom, and datacom applications. Each channel has an independent multi-rate CDR capable of operating at data-rates between 42 Mbps and 3.2 Gbps, allowing maximum flexibility in system design. The M21011 is rated for operation in the range of 1 Gbps to 3.2 Gbps. The M21001 is rated for operation in the range of 42 Mbps to 800 Mbps. Aside from the difference in supported signal data-rates, the M21012, M21011, and M21001 are identical. Signal conditioning features include input equalization and output pre-emphasis, allowing robust reception and transmission of signals to other devices up to 60" away. User-selectable input interface types allow DC-coupled input to CML, LVDS, and LVPECL. The outputs can also be DC-coupled to CML and LVDS. Frequency acquisition is accomplished with an external reference clock. The built-in frequency synthesizer allows multi-rate operation, while operating with a single reference clock. The device can be controlled either through hardwired pins or an I<sup>2</sup>C -compatible interface. The hardwired mode eliminates the need for an external microcontroller, while allowing control of the key features of the device. The I<sup>2</sup>C-compatible interface allows complete control of the device features

#### **Applications**

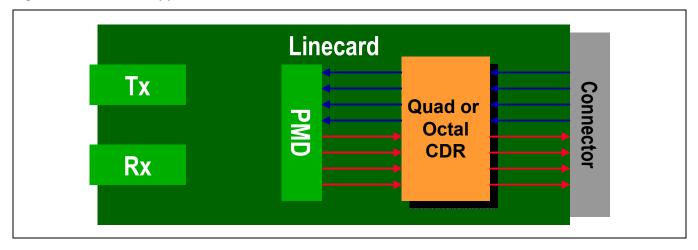

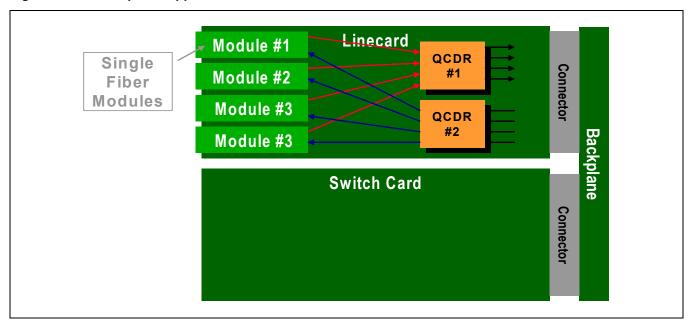

- · Backplane reach extension

- · SONET OC-48, OC-48 with FEC systems and modules

- · Fibre Channel systems

- Gigabit Ethernet systems

- 10GBASE-CX4 systems and modules

- · Clock Synthesizer

#### **Features**

- M21012 has four independent Multi-Rate CDRs capable of running between 42 Mbps and 3.2 Gbps

- M21011 has four independent Multi-Rate CDRs capable of running between 1 Gbps and 3.2 Gbps

- M21001 has four independent Multi-Rate CDRs capable of running between 42 Mbps and 800 Mbps

- · Flexible DC-Coupled input interface to CML, LVPECL, and LVDS

- Flexible Control through I<sup>2</sup>C-compatible interface or hardwired pins

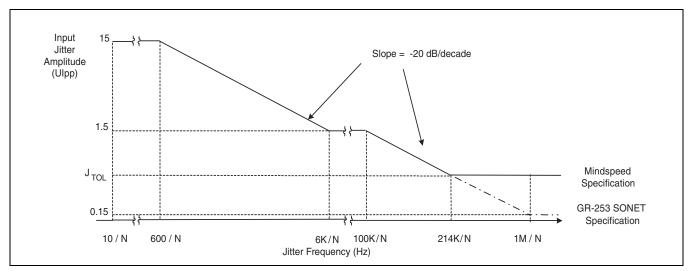

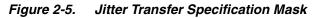

- Jitter generation 4.5 mUI rms, Jitter Tolerance 0.625 UI typical

- Signal conditioning features for superior performance on FR4 trace lengths of up to 60", twinaxial cable lengths of up to 25m

- Typical Total Power Consumption as low as 400 mW with all channels running

- · Built-in pattern generator and receiver for module and system testing

#### **Functional Block Diagram**

# **Ordering Information**

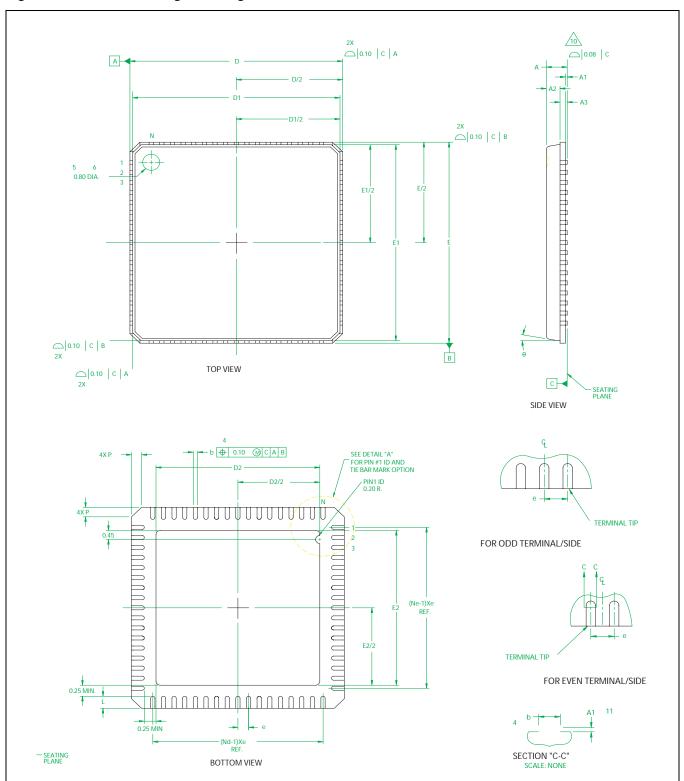

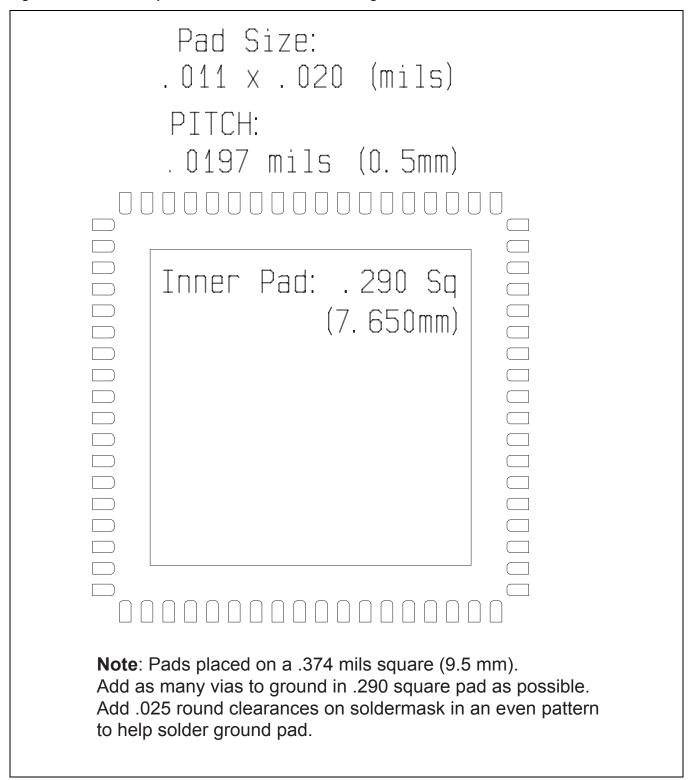

| Part Number               | Package                                    | Operating Data Rate |

|---------------------------|--------------------------------------------|---------------------|

| M21012-12                 | 72-terminal, 10mm, MLF                     | 42 Mbps - 3.2 Gbps  |

| M21012G-12 <sup>(1)</sup> | 72-terminal, 10mm, MLF<br>(RoHS compliant) | 42 Mbps - 3.2 Gbps  |

| M21011-12                 | 72-terminal, 10mm, MLF                     | 1 Gbps - 3.2 Gbps   |

| M21011G-12 <sup>(1)</sup> | 72-terminal, 10mm, MLF<br>(RoHS compliant) | 1 Gbps - 3.2 Gbps   |

| M21001-12                 | 72-terminal, 10mm, MLF                     | 42 Mbps - 800 Mbps  |

| M21001G-12 <sup>(1)</sup> | 72-terminal, 10mm, MLF<br>(RoHS compliant) | 42 Mbps - 800 Mbps  |

#### NOTES:

- 1. The letter "G" designator after the part number indicates that the device is RoHS-compliant. Refer to www.mindspeed.com for additional information.

- 2. M21012, M21011, M21001 are the base device numbers, and -12 is the device revision number.

- 3. These devices are shipped in trays.

# **Revision History**

| Revision | Level   | Date          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D        | Release | November 2005 | <ul> <li>Discontinued support for LVPECL output interface.</li> <li>Added note about reserved two-wire serial interface addresses 00001xx.</li> <li>Updated Table 2-1 with absolute maximum ratings for high-speed signal, control, interface, and alarm pins.</li> </ul>                                                                                                                                                                                                                  |

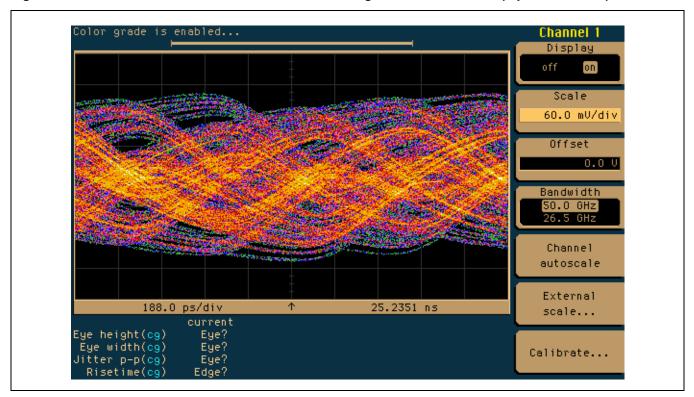

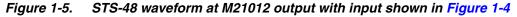

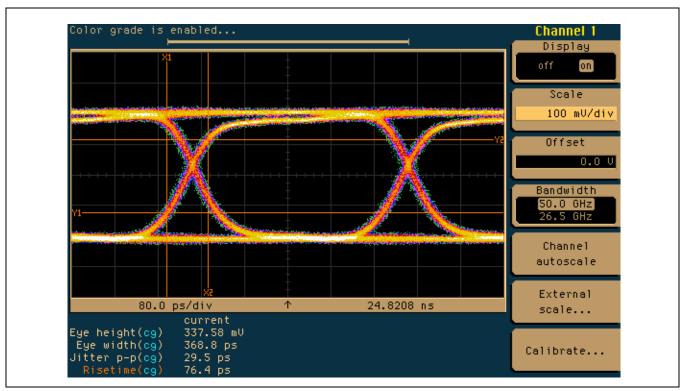

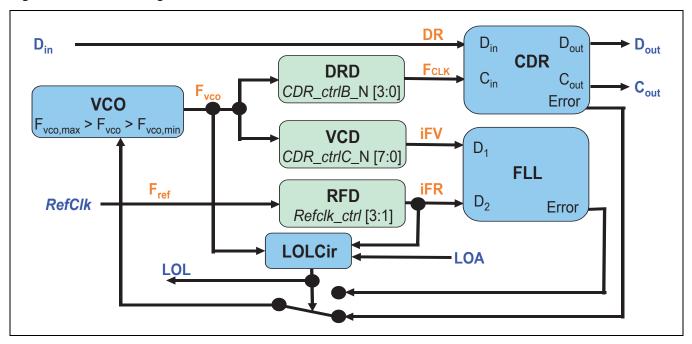

| С        | Release | July 2005     | <ul> <li>Added RoHS compliant part numbers to the ordering information.</li> <li>Table 2-2 note 4 updated to reflect 0°C ≤ T<sub>a</sub> ≤ 70°C for F<sub>VCO</sub> &gt; 2.666 GHz.</li> <li>Added Section 1.2.15 to provide details on supported ambient temperature range as a function of data-rate.</li> <li>Included figure "Definition of Pre-Emphasis Levels" in Section 1.2.11</li> <li>Inserted eye diagrams in Section 1.2.10 showing input equalization performance.</li> </ul> |

# **Table of Contents**

|     | Orde | ering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | į  |  |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

|     | Revi | sion History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i  |  |  |  |

|     | Tahl | e of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ii |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     | List | of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ١  |  |  |  |

|     | List | of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ٧  |  |  |  |

| 1.0 | Fund | ctional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1  |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     | 1.2  | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      | 1 2 8 Two-Wire Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ٠, |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      | 1.2.12 CDR Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

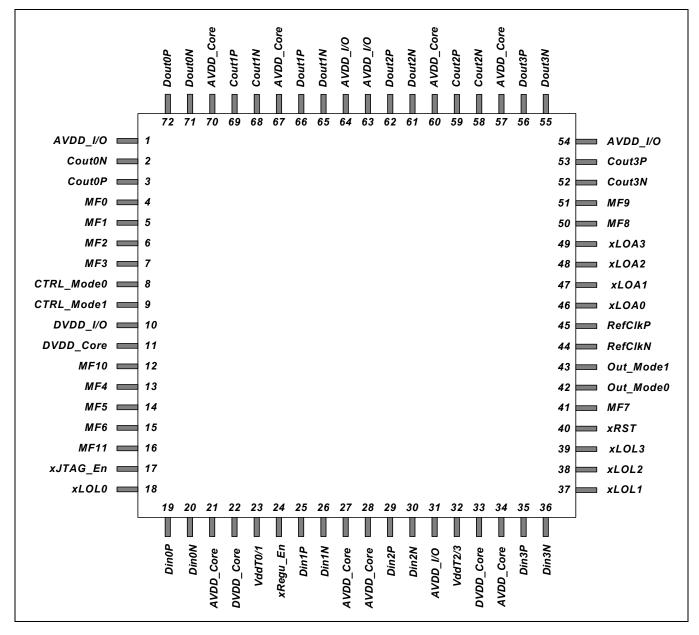

|     | 1.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

| 0.0 | Dros |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

| 2.0 | Proc | 1.1 Applications       .1         1.2 Detailed Feature Descriptions       .4         1.2.1 Conventions       .4         1.2.2 Reset       .2         1.2.3 Internal Voltage Regulator       .4         1.2.4 High-Speed Input/Output Pins       .2         1.2.5 CDR Reference Frequency       .6         1.2.6 Multifunction Pins Overview       .6         1.2.7 Multifunction Pins Defined for Hardwired Mode.       .7         1.2.8 Two-Wire Serial Interface.       .8         1.2.9 JTAG       .9         1.2.10 Input Deterministic Jitter Attenuators.       .9         1.2.11 Output Pre-Emphasis       .1         1.2.12 CDR Features       .1         1.2.13 Multi-Rate CDR Data-Rate Selection       .1         1.2.14 Frequency Reference Acquisition (FRA)       .1         1.2.15 Ambient Temperature Range Limitations       .1         1.2.17 Built-In Self Test (BIST) Overview       .1         1.2.18 BIST Test Patterns       .1         1.2.20 BIST Transmitter (BIST Tx) Operation       .16         1.2.21 Junction Temperature Monitor       .1         1.2.22 IC Identification / Revision Code       .15         1.3 Pin Definitions       .2         2-1 Absolute Maximum Ratings       .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |

|     | 2.1  | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24 |  |  |  |